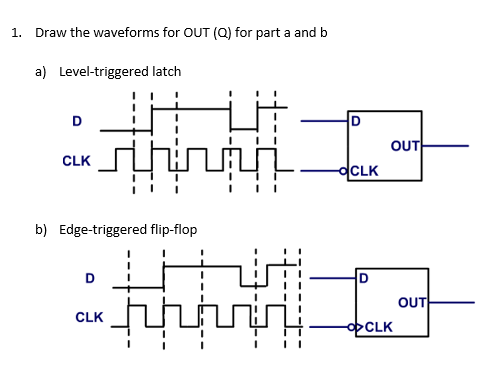

The more we slow down the clock, the more time we allow for unrestricted feedback. In level triggering, slowing down the clock works against us. We also want the nice property that we can slow down the clock, and not have the sequential circuit break. In sequential circuits, we want the outputs produced in clock period \$t\$ to only come into consideration for computing the states of clock period \$t + 1\$. So by the time the well-defined moment occurs when the clock falls and every device is supposed to snapshot and hold it state until the next level, chaos has already occurred and the circuits are in unpredictable states. In circuits that have feedback (the outputs are connected back to the inputs) level triggering causes chaos, because the level is wide enough (half a clock cycle) that the output can feed back to the inputs within the same period. The issue with level triggering is that while the clock level is high, inputs change the outputs. There is a well-defined moment in time when the level of the clock falls, the inputs to the clocked circuit are sampled, and further changes in inputs are no longer admitted. What is the feedback problem?īut how will it be solved in edge triggering? If the time for falling or rising is very short, how will the output be able to propagate through all gates? Is it like, once edge triggering is applied the output will be propagate through all gates and next inputs will be considered only at the next clock edge ?Īlthough an edge is a well-defined moment in time, it is not true to say that level-triggering also does not have a well-defined moment in time. Secondly, the feedback problem, since the level triggering duration is long as compared to the edge triggering, in the case of the former, the output would be fed back again to the input and it will keep doing this as long as the clock is active. I did not understand why the output would not rush in level triggering and why we need a short pulse to hold the output.

The feedback problem is solved because there's insufficient time for the new output to race back to the input within duration of a single rising edge" But such short pulse is not easy to create, hence we go for edge triggering. To avoid this we need an short pulse to capture the output and hold it constant.

"If the clock is level sensitive, the new \$Q_n\$ can rush through the logic network and change the output. What does it mean?Īlso I am not able to understand the following: After searching online I came to know that edge triggering is insensitive to glitches whereas level triggering is sensitive. I am trying to understand why edge triggering is preferred over level triggering.

0 kommentar(er)

0 kommentar(er)